Snapback breakdown ESD device based on zener diodes on silicon-on-insulator technology - ScienceDirect

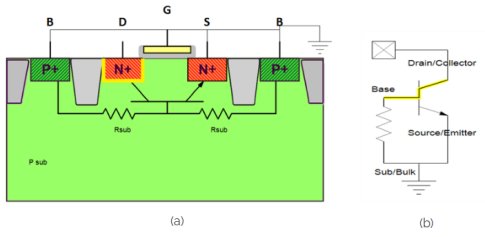

Figure 1 from Modeling MOS snapback for circuit-level ESD simulation using BSIM3 and VBIC models | Semantic Scholar

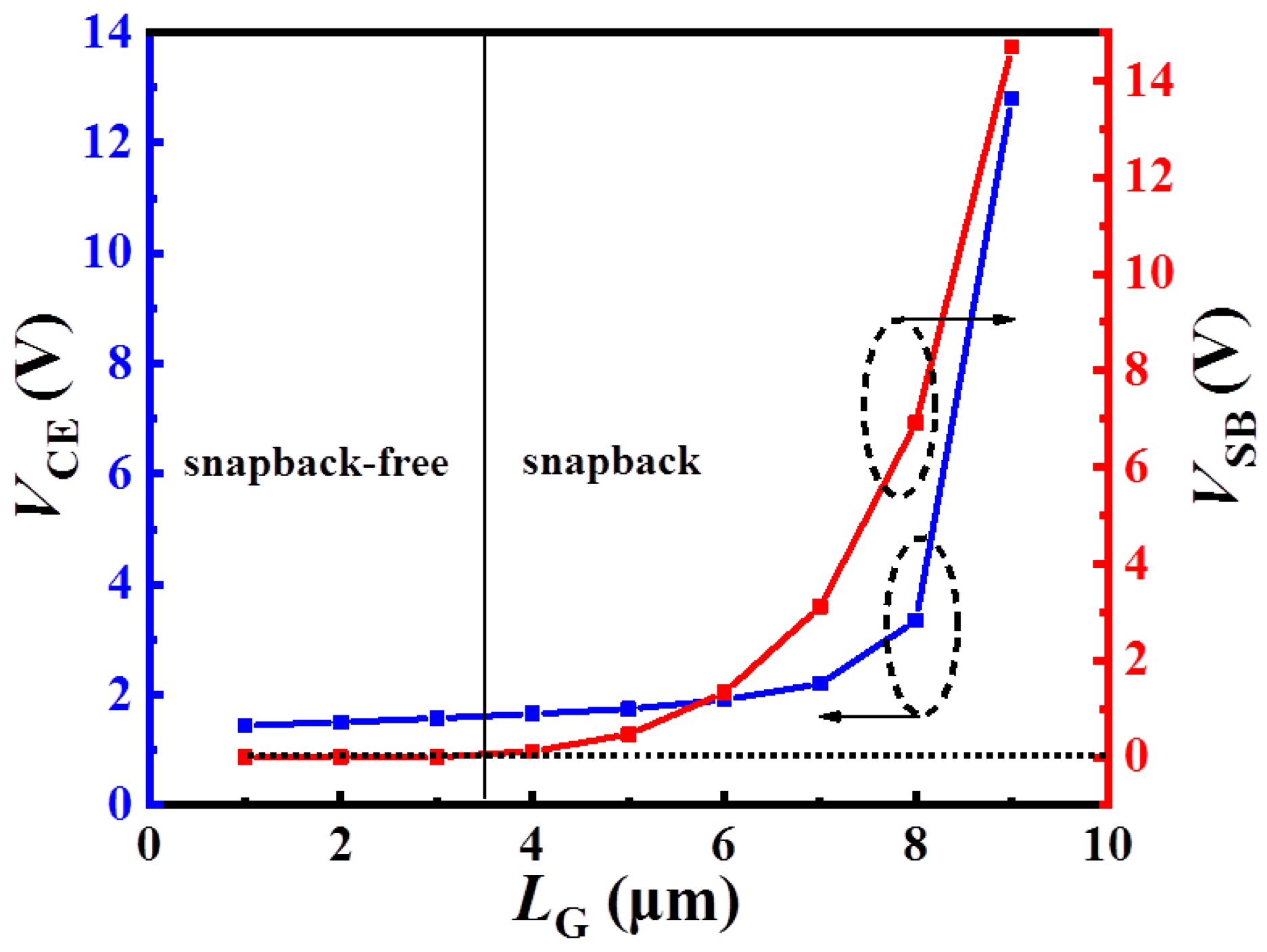

Bipolar effects in snapback mechanism in advanced n-FET transistors under high current stress conditions

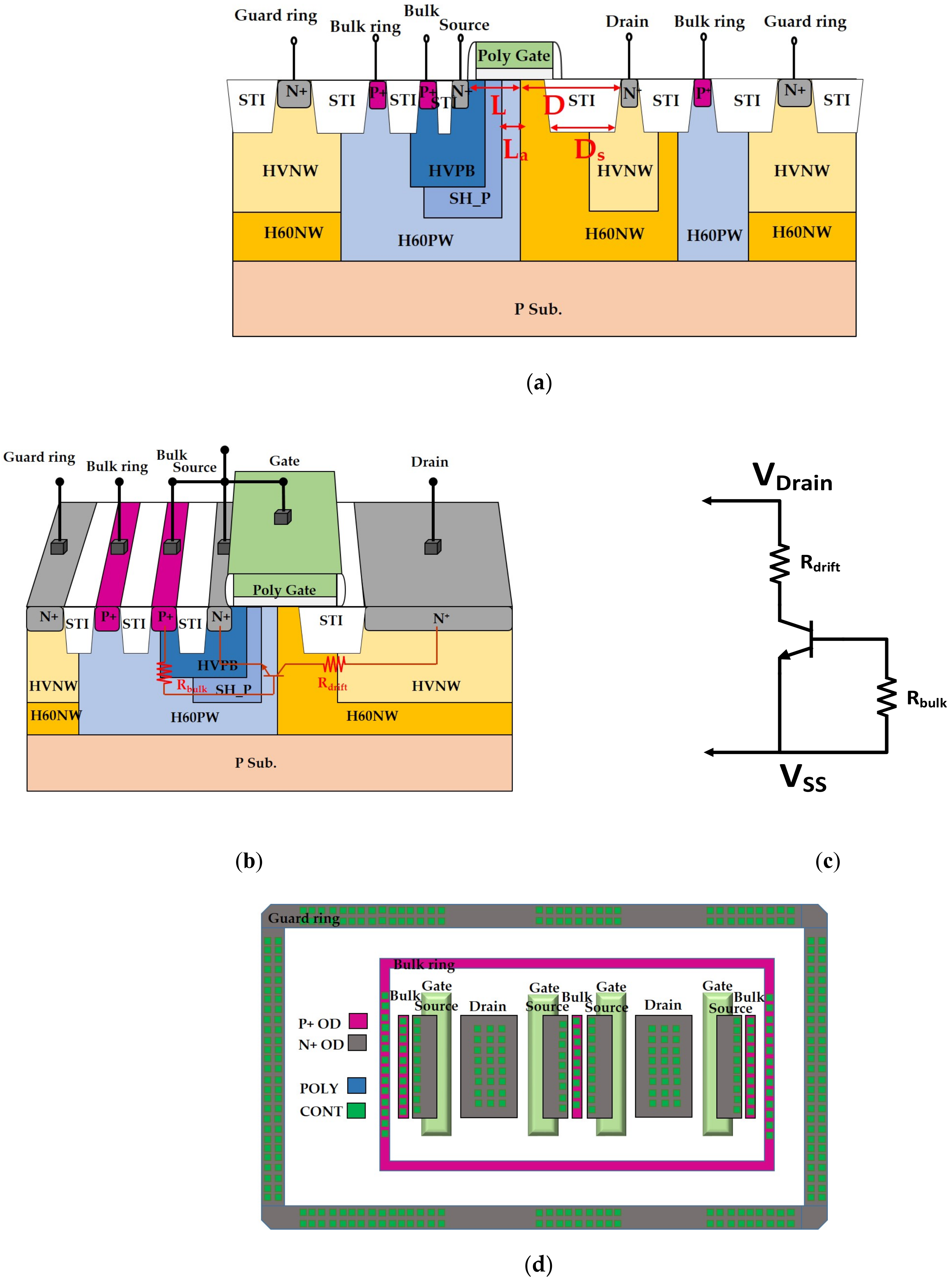

Electronics | Free Full-Text | Simulation Study of Low Turn-Off Loss and Snapback-Free SA-IGBT with Injection-Enhanced p-Floating Layer

Modeling MOS snapback and parasitic bipolar action for circuit-level ESD and high current simulations | Semantic Scholar

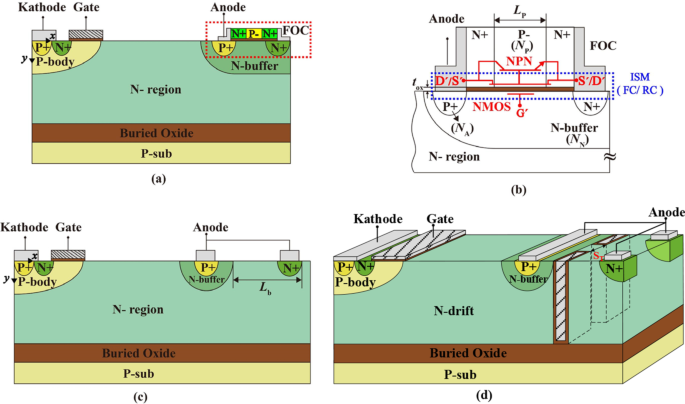

Snapback breakdown ESD device based on zener diodes on silicon-on-insulator technology - ScienceDirect

Figure 1 from A Study of Snapback and Parasitic Bipolar Action for ESD NMOS Modeling | Semantic Scholar